0. 목차

- '반도체 공정'이란?

- '반도체 공정' 산업의 특징

- 반도체의 주요 8대 공정

- 반도체 3D 공정 및 기술 발전방향

- 국내의 반도체 산업

- '반도체 공정' 관련 기업

1. '반도체 공정'이란?

'반도체(Semiconductor)'는 전자 및 통신, 기계 분야 등의 첨단 산업화를 위해 반드시 필요하다. '반도체(Semiconductor)'는 '웨이퍼(Wafer)' 표면에 수천만 개의 트랜지스터 등을 형성시키는 '플레이너(Planar)' 기술을 통해 생산되고 있다. 즉, 수천만 개의 전자 부품과 회로 연결 부분을 미세화 공정을 통해 설계한 다음, 이 설계도를 담은 '포토마스크(Photomask)'를 웨이퍼 위에 놓고 자외선을 투과해서 웨이퍼 상에 반도체 회로를 새겨 넣는 기술을 기반으로 반도체가 제작된다.

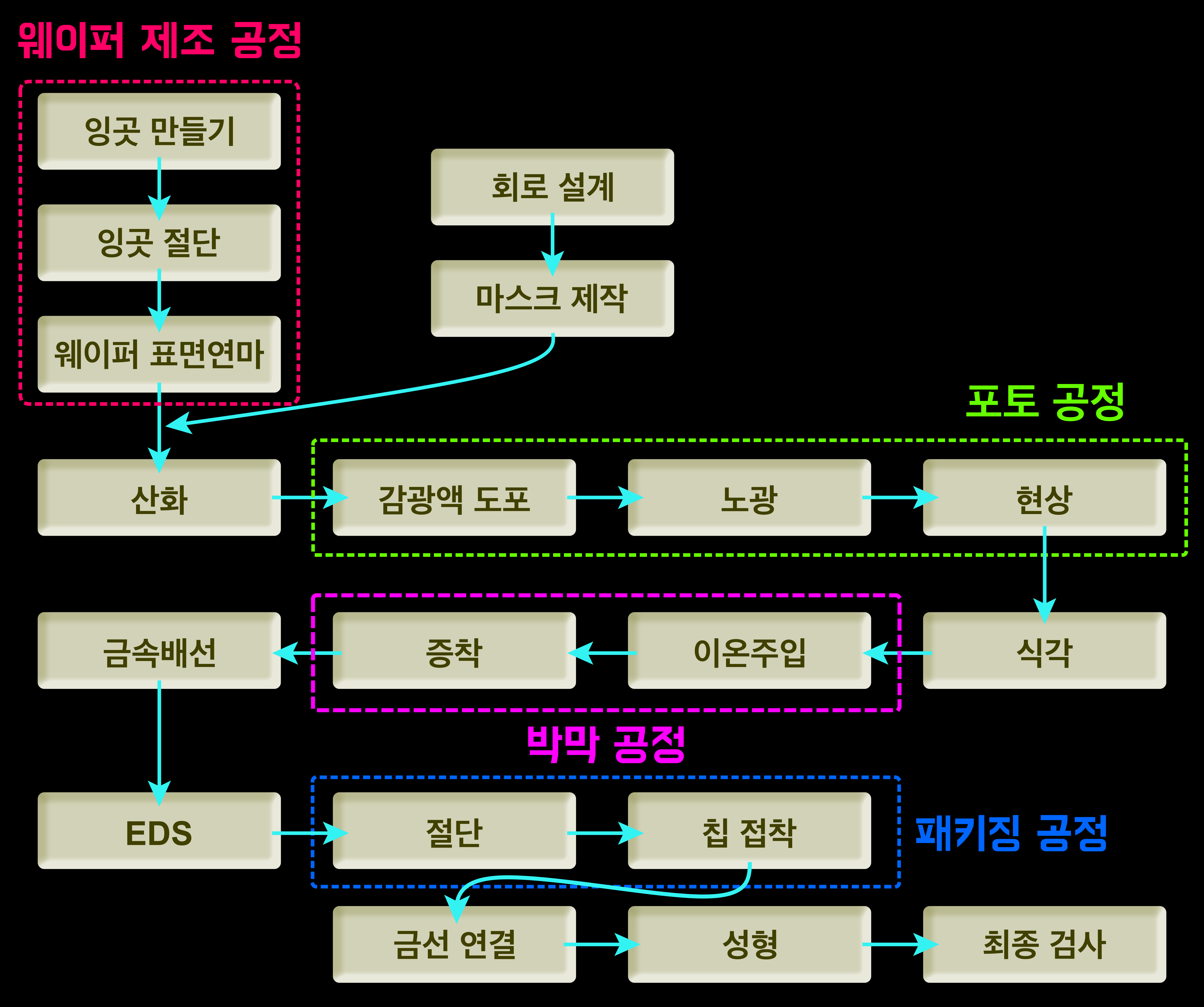

반도체는 웨이퍼 가공·조립 과정을 거쳐 제조되며, 크게 '전공정(Front-End Process)'과 '후공정(Back-End Process)'으로 구분된다. '전 공정(Front-End Process)'은 웨이퍼 위에 회로를 새겨 칩을 완성하는 공정이고, '후 공정(Back-End Process)'은 전 공정을 통해 완성된 웨이퍼를 칩 단위로 절단·분리하여 패키징 한 다음 테스트하는 공정이다. '반도체 전 공정'은 '감광막 도포', '노광(Exposure)', '식각(Etching)', '현상', '이온 주입', '증착(Deposition)' 공정 등이 반복되면서 진행되고, '반도체 후공정'은 전 공정이 완료되어 웨이퍼에 회로가 형성된 다음 'Burn in Test', '절단', '패키징(Pacakaging', '최종 검사' 등을 수행하는 것이다.

2. '반도체 공정' 산업의 특징

'반도체 공정' 산업은 '전자', '통신', '정보' 산업 부문과 함께 지속적으로 발전하고 있는 산업으로서, 국내외 유수 업체들이 다수 참여하여 경쟁력 있는 산업 생태계를 구축하고 있다. 반도체를 생산하기 위해 대규모의 설비 투자가 요구되고, 공정 기술 자체 개발에도 많은 연구개발 투자가 소요되어, 매출액 대비 R&D 투자 비율이 타산업보다 현저히 높은 기술집약적 산업이다. 일반적으로 '반도체 소자'는 기술 발전 속도가 타산업 대비 빠르고, 제품의 수명 주기가 짧은 특성을 보이고 있다. '반도체 공정'도 기술 수명 주기가 비교적 짧은 편이고 지속적인 기술 개발이 필수적이다. 반도체 공정 산업의 특징은 '고부가가치 산업', '자본집약적 산업', '기술집약적 산업', '시장 진입장벽이 높은 산업', '경제적 파급효과가 큰 산업'으로 요약할 수 있다.

- 고부가가치 산업: 전방 산업이 '반도체 소자'의 고기능화 및 경박단소화 추세에 따라, 관련 기술 확보 여부 및 지속적인 투자 개발이 필요하다. 관련 기술 개발을 통한 국가 기술력의 제고에도 크게 관여하는 산업이다.

- 자본집약적 산업: 반도체 공정 기술 개발에 장기적인 투자가 필수적이고, 초기 설비 구축 및 생산을 위한 대규모 투자가 요구되는 산업이다.

- 기술집약적 산업: 반도체 산업 특성상 높은 수준의 품질 및 신뢰성이 요구되어 기술 중요도가 높고, 우수한 연구 인력을 필요로 하는 산업이다.

- 시장 진입장벽이 높은 산업: 기술 수준이 높고, 슈요처가 반도체 제조사로 한정적이며, 원천 기술 확보 및 막대한 자본 투자에 대한 부담이 높은 산업이다.

- 경제적 파급효과가 큰 산업: 국가의 미래 육성 산업 기술 정책에 부합하는 산업으로, 정부 차원의 활성화 및 정책 등이 지속적으로 추진되는 산업이다.

3. 반도체의 주요 8대 공정

반도체의 주원료인 '웨이퍼(Wafer)'는 주로 '실리콘(Sillicon, 규소)' 재질로 만들어진다. '웨이퍼'는 전기가 통하지 않는 부도체 상태임에 따라, 도체와 부도체의 특징을 포함한 '반도체'로 제작하기 위해서 웨이퍼에 여러 가지 화학물질을 형성시킨 후, 설계된 회로를 새기는 정밀 작업을 수행한다. 일반적으로 반도체가 웨이퍼 단계에서부터 집적회로 소자가 되는 주요 프로세스를 '반도체 주요 8대 공정'이라고 한다.

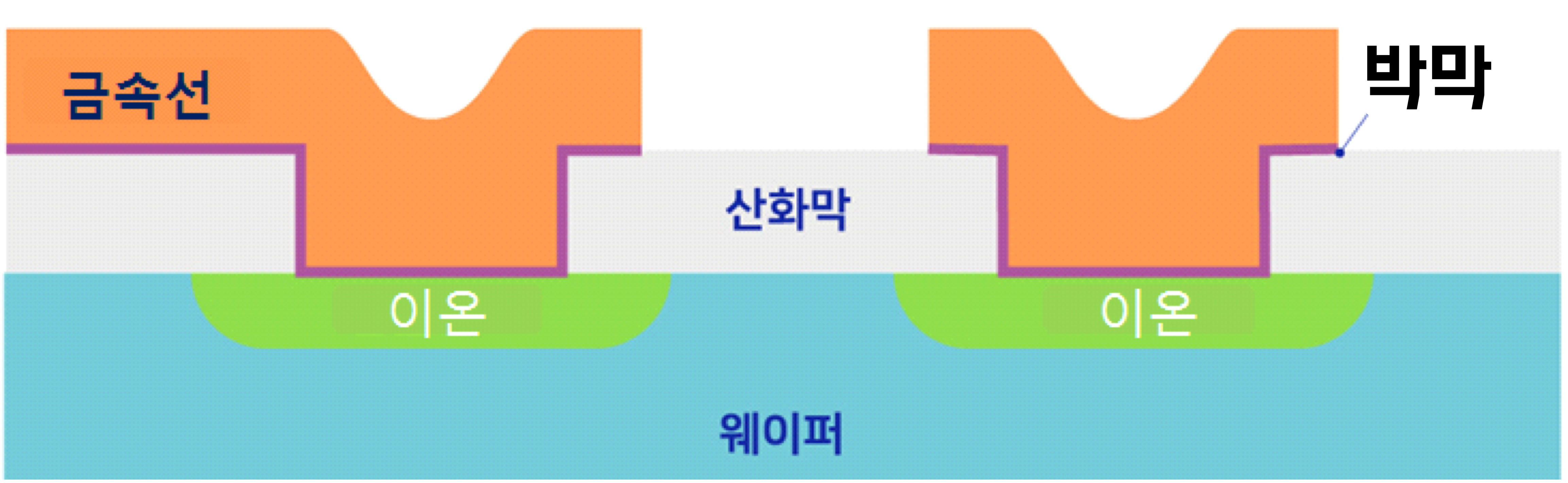

8대 공정 중에서 '웨이퍼 제조', '산화', '포토', '식각', '박막(Thin Film, 기계가공으로는 실현 불가능한 두께 μm 이하의 엷은 막)', '금속배선' 공정이 반도체 '전 공정(Front-End Process)' 단계에 포함되고, 이후 '후 공정(Back-End Process)'' 단계에는 'EDS(Electrical Die Sorting)' 공정과 '패키징(Packaging)' 공정을 통해 완제품이 생산된다. 즉, 반도체 전 공정은 웨이퍼 위에 화학 물질층을 '적층(Lamination)'하고, 회로 미세 패턴을 형성하며, 필요 없는 부분을 제거하는 등, 다양한 공정을 거쳐 웨이퍼 상에 원하는 소자를 구현하는 과정으로서, FAB 공정이라고 한다. 반도체 후공정은 웨이퍼 위에 구현된 다수의 소자를 개별 단위로 자른 다음 분리해서, 실제 사용이 가능한 완제품 형태로 만드는 과정이다. '양품(질이 좋은 제품)'을 생산하기 위해, 모든 반도체 제조 과정에서 제품의 품질·성능을 확인하는 검사 공정도 수반된다. 8대 공정을 단계별로 살펴보면 다음과 같다.

| 분류 | 반도체 8대 공정 |

| 전공정 (Front-End Process) | 웨이퍼 제조 |

| 산화 공정 | |

| 포토 공정 | |

| 식각 공정 | |

| 박막 공정 | |

| 금속배선 공정 | |

| 후공정 (Back-End Process) | EDS 공정 |

| 패키징 공정 |

3-1. 웨이퍼 제조

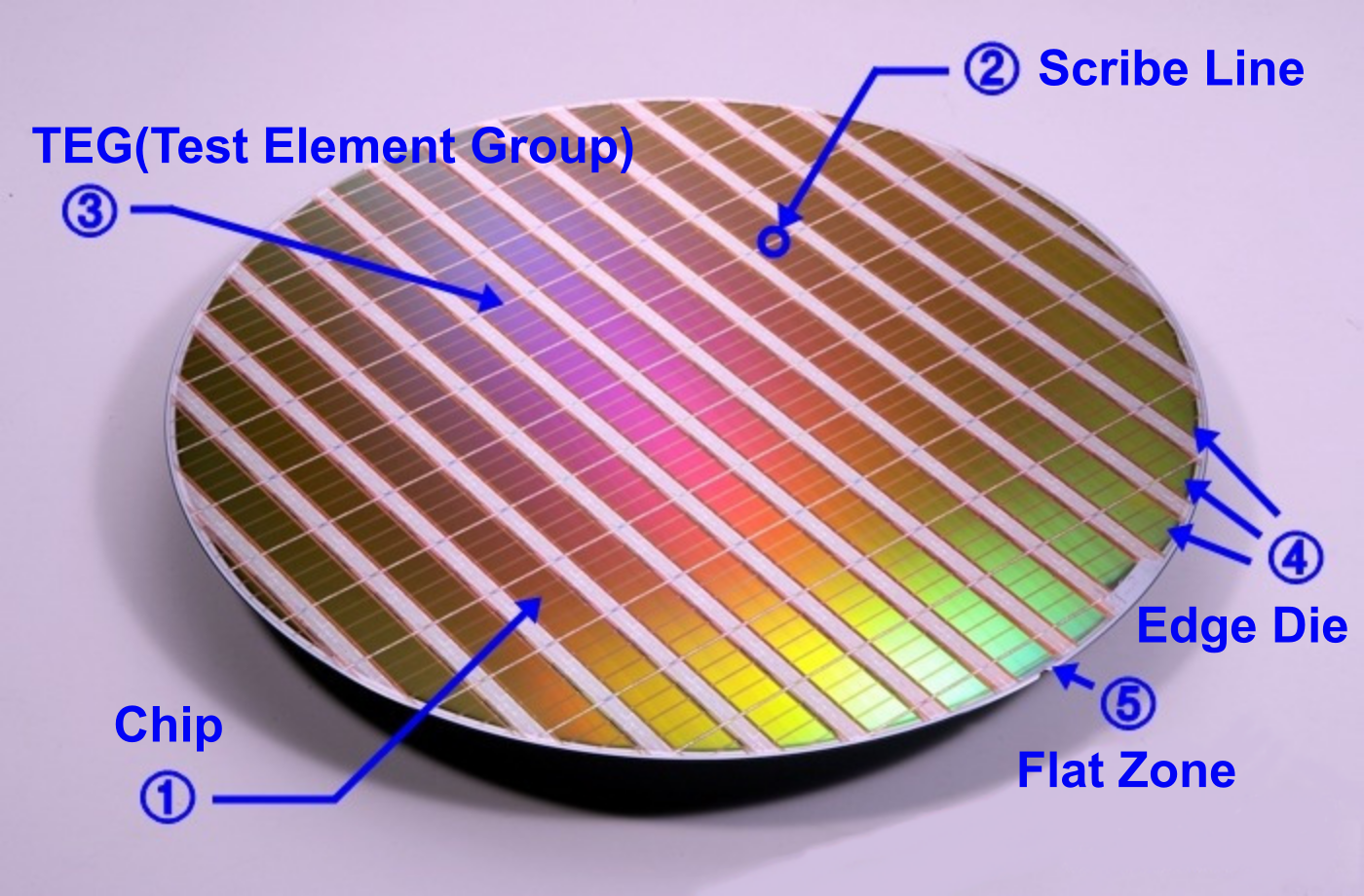

반도체의 기본인 '웨이퍼(Wafer)'는 독성이 없고 고온에서 견딜 수 있으며, 모래에서 추출할 수 있는 '실리콘(Silicon, 규소)'을 주원료로 한다. 실리콘을 뜨거운 열로 녹여 고순도의 용액을 생성하고 '결정 성장 장치'를 통해 실리콘 기둥 형태인 '잉곳(Ingot)'을 만든 다음, 다이아몬드 톱을 이용해 균일한 두께로 자른다. 그리고 웨이퍼의 표면을 '연마액(Polishing Liquid)'과 '연마 장비(Polishing Machine)'을 통해 매끄럽게 정밀 가공한다.

- Chip: 웨이퍼 위 전자회로가 새겨진 얇고 작은 조각으로, IC칩이 되는 부분이다.

- Scribe Line: Chip 사이의 경계로, 아무 전자회로가 없는 부분이며, 웨이퍼를 개개의 칩으로 나누기 위한 분리 선이다.

- TEG(Test Element Group): 작은 IC칩 한 개에는 수십만 또는 수백만 개의 트랜지스터, 캐퍼시터, 저항, 다이오드, 배선 회로 등으로 구성되어 있어 실제 칩의 동작 여부를 판단하기 위해 테스트가 필요하다. 따라서 칩의 실제 특성을 보기 위해 패턴을 구현한 것이 TEG이다.

- Edge Die: 웨이퍼는 가장자리 부분에 손실 부분, 즉 '다이(Die)'를 가진다. 직경이 작은 웨이퍼보다 큰 웨이퍼의 다이 부분이 적고 손실률도 줄어든다.

- Flat Zone: 웨이퍼 결정 구조는 눈으로 식별이 불가능하다. 따라서 웨이퍼의 구조를 판별하기 위해 웨이퍼의 한 부분을 평평하게 만드는데, 이를 '플랫존(Flat Zone)이라고 한다.

3-2. 산화 공정(Oxidation Process)

'산화 공정(Oxidation Process)'에서는 만들어진 웨이퍼를 외부의 오염물질로부터 보호하기 위해서, 웨이퍼 표면에 산소 또는 수증기를 웨이퍼 표면에 뿌려 넣고, 절연막 역할을 하는 '산화막(SiO2)'을 형성한다. '산화막'은 회로 사이에 뉴설전류가 흐르는 것을 차단하고, '식각공정' 상에서 필요한 부분이 잘못 식각되는 것을 방지한다. 1000℃ 이상의 고온에서 얇고 균일한 실리콘 산화막을 형성시키는 '열산화 방식'이 주로 사용되며, '건식 산화 방식'과 '습식 산화 방식'이 있다.

3-3. 포토 공정(Photo Process)

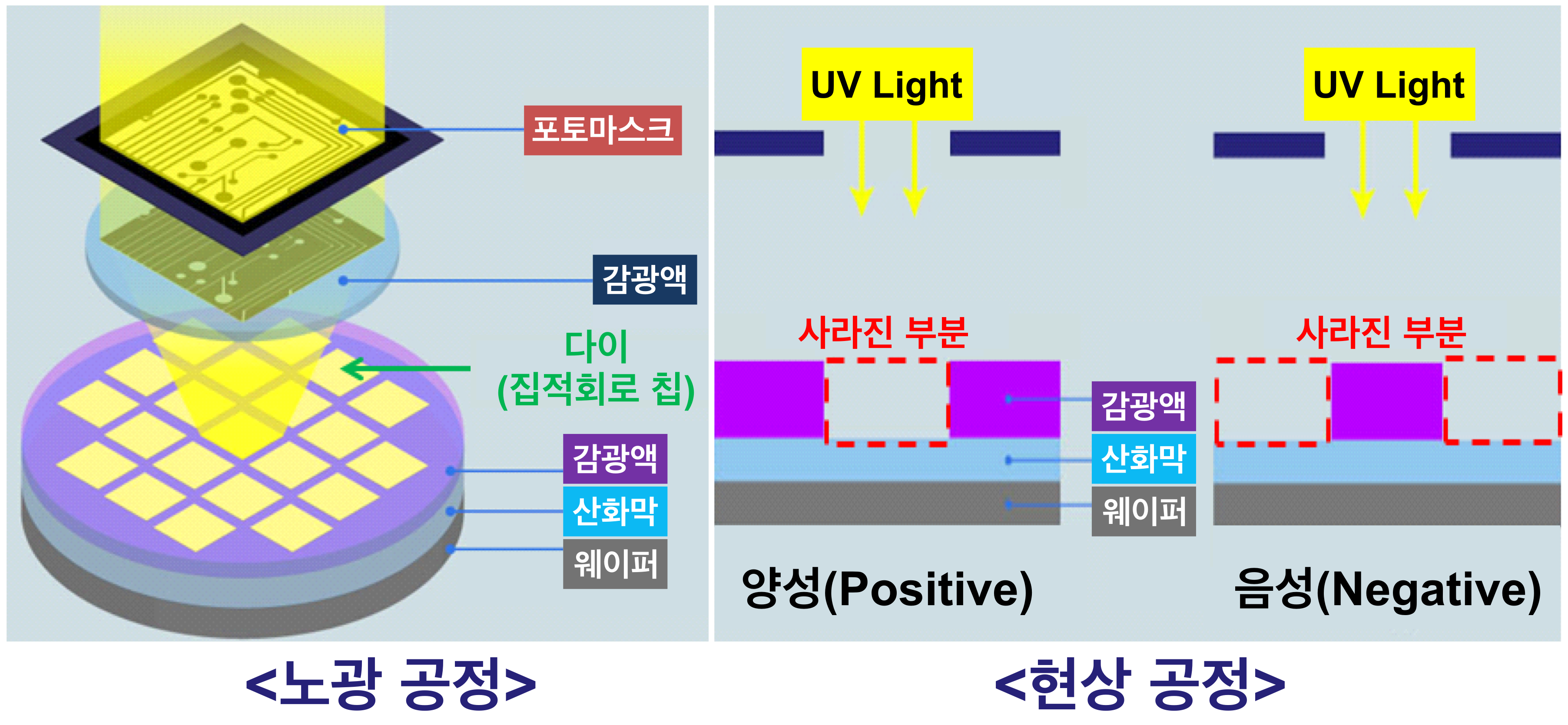

'포토 공정(Photo Process)'은 산화막이 생성된 웨이퍼에 회로 패턴이 설계되어 있는 '포토마스크(Photomask)'를 이용하여 회로를 형성하는 공정이다. '포토 공정'은 '감광액 도포', '노광 공정', '현상 공정' 등 세부 공정으로 구분된다.

- 감광액 도포: 고품질의 미세한 회로 패턴을 얻기 위해서, 웨이퍼 표면에 빛에 민감한 물질인 '감광액(PR: Photo Resist)'을 얇고 균일하게 도포하여 빛에 대한 감도를 높이는 것이 중요하다.

- 노광 공정: '감광막(PR)'을 형성해서 웨이퍼를 사진의 인화지와 유사한 상태로 만든다. 이후, 회로 패턴이 담긴 '포토마스크(Photomask)'에 빛을 통과시키고, 렌즈를 통해 웨이퍼의 집적회로 칩인 '다이(Die)'에 적합하도록 회로 크기를 축소해서 웨이퍼 상에 형성하는 '노광 공정'을 진행한다.

- 현상 공정: 그다음 웨이퍼에 현상액을 투여해서 '노광된 영역'과 '노광되지 않은 영역'을 선택적으로 제거해, 마스크에 설계하였던 '회로 패턴'을 웨이퍼 상에 현상한다. 참고로, '감광액'은 빛에 어떻게 반응하는가에 따라 '양성(Positive)' 혹은 '음성(Negative)'으로 분류된다. '양성 감광액'의 경우 노광된 영역이 사라지고, '음성 감광액'의 경우 노광된 영역만 남는다.

3-4. 식각 공정(Etching Process)

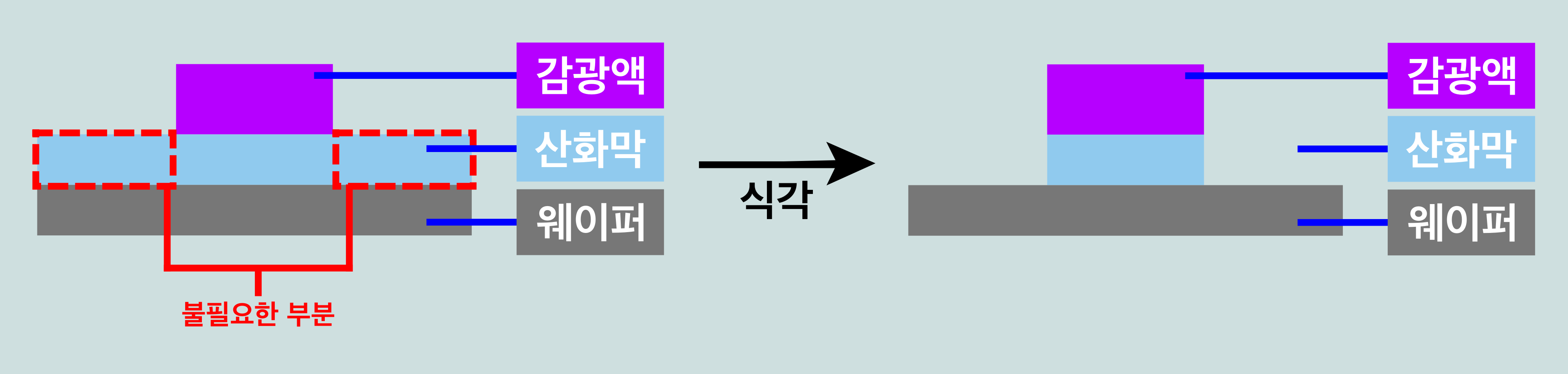

회로 패턴을 웨이퍼에 새겼으면, 화학물질 액체 또는 기체를 통해 필요 없는 부분을 제거하는 '식각 공정(Etching Process)'을 진행한다. 가스로 식각하는 '건식 방식'은 '습식 방식'에 비해 기술적으로 난이도가 높고, 제조 공정 상에서 단가가 상대적으로 많이 투입된다. 하지만 '건식 방식'은 회로의 선폭이 나노 단위로 얇아지면서 수율을 높이기 위한 방법으로 주목받고 있다. '식각 공정'시 일정한 시간 동안 웨이퍼 상의 여러 지점에서 식각 속도가 균일하게 이루어져야 특정 부위에 위치한 칩의 불량률을 최소화할 수 있음에 따라 '균일도' 및 '식각 속도' 등을 정밀하게 관리하는 것이 매우 중요하다.

3-5. 박막 공정

반도체에 필요한 전기적 특성을 갖추기 위해 웨이퍼 위에 '박막(Thin Film, 기계가공으로는 실현 불가능한 두께 μm 이하의 엷은 막)'을 형성한다. '박막(Thin Film)'을 만드는 '증착 공정'은 '물리적 기상 증착법(PVD: Physical Vapor Deposition)'과 '화학적 기상 증착법(CVD: Chemical Vapor Deposition)' 등이 있다. 이 중에서 두께 균일도를 조절할 수 있으며, 대량 처리가 가능한 플라즈마 '기상 증착 방법(CVD)'이 주로 사용되고 있다. 박막은 크게 회로 간의 전기적인 신호를 연결해주는 '금속막의 '전도층'과, 내부 연결층을 전기적으로 분리하거나 외부 오염물질로부터 차단시키는 '절연막층(Insulator Film Layer)'으로 구분된다. 그리고 박막 공정시 미세한 가스 입자인 이온 '인(P)', '비소(As)', '붕소(B)'를 주입해서 반도체가 전도성을 갖도록 '이온 주입 공정(Ion implantation Process)'을 수행한다.

3-6. 금속배선 공정

일반적으로 반도체를 구동시키기 위해 외부에서 전기적 신호를 인가해 주어야 하며, 전기신호가 원활하게 흐르도록 반도체 회로 패턴을 따라 금속선을 형성시키는 작업을 한다. 고온과 화학적인 반응에서도 금속 고유 특성이 변하지 않는 '알루미늄(Al)', '티타늄(Ti)', '텅스텐(W)' 등이 주로 사용되고, 미세한 반도체 회로에 형성되어야 하므로 '금속배선 공정'을 진행한다.

3-7. EDS 공정

'전 공정(Front-End Process)'을 통해 제작된 반도체 칩을 웨이퍼 상태에서 테스트하는 'EDS 공정'은 'ET/WBI (Electrical Test/Wafer Burn In)', 'Hot/Cold 테스트', 'Repair/Final 테스트', '잉킹(Inking)' 등 세부 공정으로 구성된다.

- ET/WBI (Electrical Test/Wafer Burn In): ET는 반도체 칩을 구성하는 개별 소자인 '트랜지스터', '저항', '캐패시터', '다이오드' 등에 '직류전압', '전류' 등을 인가하여 동작 여부를 테스트하는 과정이다. WBI 공정은 웨이퍼에 일정 온도의 열을 가한 다음 AC/DC 전압을 인가해서 잠재적인 불량 요인을 판별하는 테스트이다.

- Hot/Cold 테스트: 그리고 상온보다 높고, 낮은 온도에서 반도체 칩이 정사 동작하는지 판별하기 위해 'Hot/Cold 테스트'를 수행한다.

- Repair/Final 테스트: 테스트 중에서 수리 가난하다고 판정된 칩은 수선한 다음 재차 검증하여 '양품(질이 좋은 제품)'을 최종 판단한다.

- 잉킹(Inking): EDS 공정에서 최종 테스트 후에 불량품으로 선별된 반도체 칩에는, 특수 잉크를 찍어 육안으로도 불량을 식별할 수 있도록 하고, 향후 제조 공정에 투입되지 않음에 따라 전반적인 생산 수율을 높이는 데 기여한다.

3-8. 패키징 공정

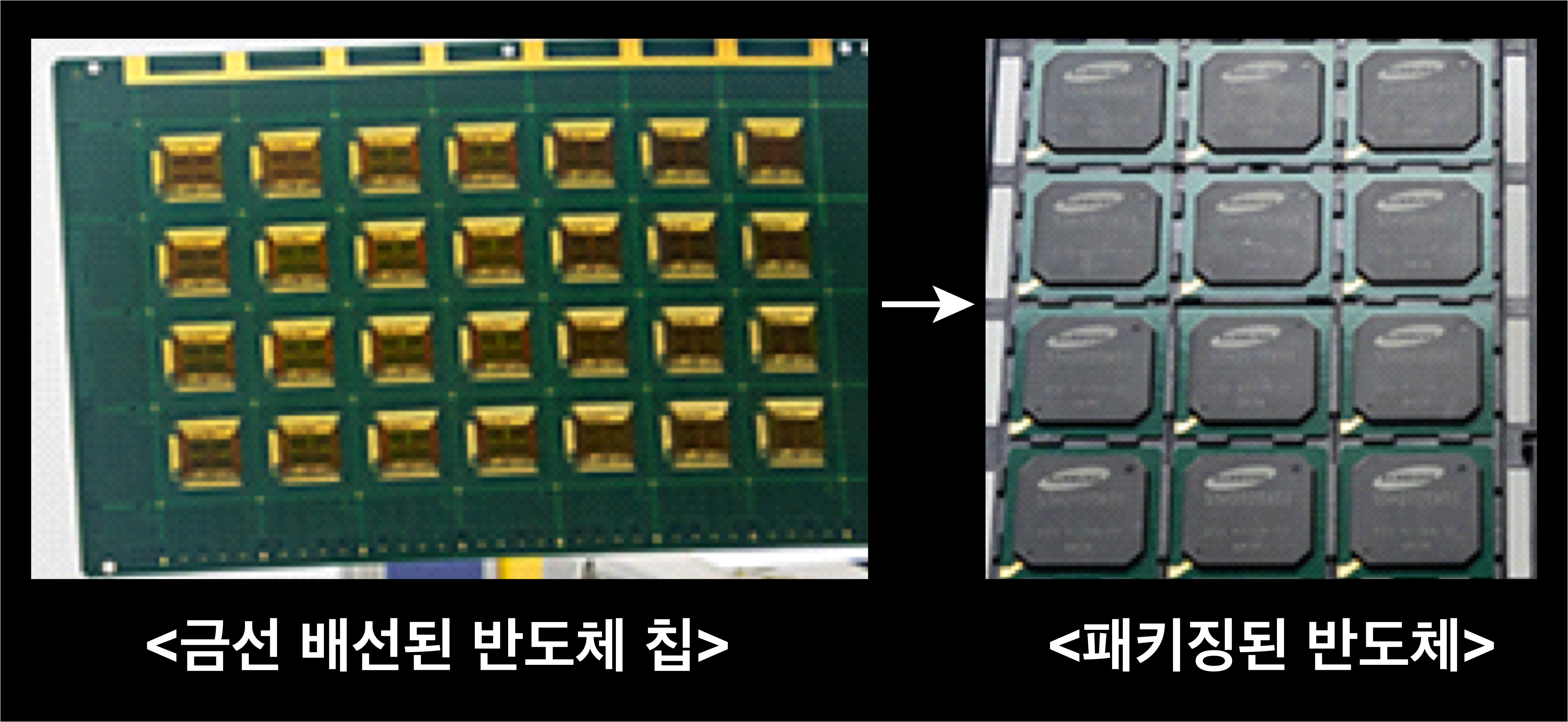

EDS 공정을 통해 '양품(질이 좋은 제품)'으로 판별된 웨이퍼 상의 반도체 칩은 절단 공정을 통해 낱개로 분리된다. 그리고 반도체 칩과 외부 회로 간 전기신호를 전달할 수 있는 '인쇄 회로 기판(PCB: Printed Circuit Board)'에 칩을 접착한다. '칩'과 ''인쇄 회로 기판(PCB)'의 전기적 연결을 위해 금선을 사용하여 '와이어 본딩(Wire Bonding)'을 하거나, 볼 형태의 '범프(금 또는 솔더 재질)'을 사용해서 '플립 칩(Flip Chip)' 방식을 통해 결합시킨다.

'칩(Chip)'과 '인쇄 회로 기판(PCB: Printed Circuit Board)' 연결 공정이 완료되면 '열', '습기' 등의 물리적인 외부 환경 및 충격 등으로 반도체 칩을 보호하기 위해서 '에폭시 수지(Epoxy Resin)'를 이용해 패키징 하는 과정을 수행한다. '패키징 공정(Packaging Process)'이 완료된 반도체는 검사 장비를 통해 다양한 조건의 '전기신호(전압, 전류 등', '온도', '습도' 등을 적용하여 '전기적 특성', '기능적 특성', '동작 속도' 등을 측정하고 최종 '양품(질이 좋은 제품)'을 판별한다.

4. 반도체 3D 공정

'웨이퍼 당 생산 효율'을 높이고 반도체 성능을 향상시키기 위해, 회로 패턴의 '선폭 미세화 기술'이 지속적으로 개발되고 있다. '회로 패턴(Circuit Pattern)'의 선폭이 줄어들면 반도체 칩의 크기가 작아서 웨이퍼 당 많은 칩을 생산할 수 있고, 저항이 감소하여 전력 소모도 감소시킬 수 있다. 다만, 선폭을 미세화하는 기술이 물리적 한계에 다다랐고, 칩 간의 간격이 극도로 좁아지면서 누설 전자의 간섭 현상이 심화되어 데이터 손실이 발생하게 된다. 이러한 문제를 해결하기 위해서 3D 구조로 반도체 칩을 제조하는 기술이 개발되고 있다.

- '낸드 플래시 메모리' 3D 공정: 2013년부터 '낸드 플래시 메모리(NAND Flash Memory)'는 3D 제조 방식이 도입되었다. 한 웨이퍼 상에 90단 이상까지 적층해서 생산할 수 있는 V-NAND 기술이 상용화되었다. 일반적으로 90단 '낸드 플래시 메모리(NAND Flash Memory)'의 종횡비는 1:70 이상이며, '바늘의 종횡비(1:47.5)'보다 얇고 길게 데이터가 이동할 수 있는 채널을 만들어야 한다. 따라서 1층부터 최상위층까지 채널 톨로를 균일하게 형성하는 'Plug 에칭 기술' 및 '상충부와 하층부의 회로 선폭 차이를 최소화하는 기술' 등이 지속적으로 개발되고 있다.

- 'DRAM' 3D 공정: DRAM은 '낸드 플래시 메모리(NAND Flash Memory)' 구조와 달라서, 한 웨이퍼 상에 반도체 칩을 적층할 수 없고, 웨이퍼 자체를 적층하는 'TSV(Through Silicon Via)' 기술을 이용하여 데이터 용량을 증대시키고 있다. 'TSV(Through Silicon Via)'는 웨이퍼의 기본 재질인 실리콘을 관통하는 구멍을 형성시켜서 다수 웨이퍼를 연결하는 기술이다. '다이'와 '다이' 사이에 수직으로 채널을 형성하여, 빈 공간에 구리 등을 채워 넣어 데이터 통로인 '전극(Electrode)'을 형성한다. 즉, '패키징(Packaging)' 공정 시적층된 웨이퍼 간에 최적화된 신호 전송 경로를 제공하며, 와이어 본딩 영역을 제거함에 따라 패키지를 최소화할 수 있다.

- '트랜지스터' 3D 공정: 반도체 칩의 소형화로 인하여, 칩의 일부 소자인 '트랜지스터(Transistor)'의 크기도 극소화되었다. 이에 트랜지스터 내의 누설 전자 현상을 보완하기 위해 Fin-FET 구조가 개발되었다. '트랜지스터(Transistor)'는 Gate에 전압이 인가되면 'Source'에서 'Drain'으로 전류가 흐르며 동작하게 ehlrh, Gate와 채널의 접점이 클수록 효율이 높아진다. Fin-FET 공정은 Fin 모양의 3D 구조를 사용해서 Gate와 채널의 접점 면적을 향상시켜서 '반도체 성능 향상' 및 '누설 전자 현상' 등을 개선시켰다.

최근 '빅데이터(Big Data)', '인공지능(AI)', '가상현실(VR)', '증강현실(AR)', '사물인터넷(IoT)', '웨어러블 스마트 기기(Wearable Smart Devices)' 등에 관련된 첨단 산업이 성장하면서, 고속으로 대용량 데이터를 처리·저장할 수 있는 반도체 수요가 증가하고 있다. 이러한 시장 환경을 반영하여, 데이터 용량을 확대하기 위해 평면 구조 상에서 미세화 공정을 이용하기보다 반도체 칩을 적층시켜 칩 간의 간격을 확보하고, 평면 구조의 물리적 한계를 극복할 수 있는 '적층 공정 방식'은 차세대 반도체 제조 기술로 각광받고 있다. '적층 공정 기술'은 '포토 공정(Photo Process)', '식각 공정(Etching Process)', '박막 공정(Thin Film Process)' 등에서 기존 평면 구조 대비 고난이도의 기술이 요구된다. 반도체 공정 장비 업체와 협력하여, '생산 수율 향상'을 위한 신기술을 지속적으로 개발하는 것이 중요하다.

5. 국내의 반도체 산업

5-1. 장비·소재 기술의 국산화

반도체 공정 기술을 국산화하기 위해서는 반도체 제조 공정별 '장비'와 '소재'의 기술 수준도 뒷받침되어야 한다. 다만, '해외 선도 기업'과 '국내 기업'의 기술 격차가 크고, 반도체 산업 특성상 이미 신뢰성을 인정받은 기존 장비·소재 등을 사용하는 경향이 높음에 따라, 선도 업체들이 시장을 주도하고 있는 실정이다. 이처럼 해외 의존도가 높은 문제점을 개선하기 위해서 '정부'와 '국내 반도체 제조사'들은 '장비(Equipment)'와 '소재(Material)'의 국산화에 심혈을 기울이고 있다.

반도체는 국내 뿌리 산업의 한 축을 담당하는 첨단 분야인 만큼, 정부 차원에서 국산화 기술 도입을 위해 정책을 지속적으로 추진하고 있다. 대기업들도 장비 소재 부품의 국산화율의 중요성을 인식하고, 중소기업과 상생을 도모하기 위해 대책을 마련하고 있다. 2019년 7월 1일에는 일본 경제산업성이 반도체 및 디스플레이 제조 핵심 소재의 수출을 제한하기로 발표하면서, 한국 경제제재에 돌입했다. 일본이 반도체 제조 공정 상에서 핵심 부품인 '포토레지스트(Photoresist)', '고순도 불화수소' 등을 수출 규제 항목으로 단행함에 따라, 국내 '파운드리(Foundry)' 업체는 반도체 소재 및 장비 부품의 국산화를 위해서 국내 제품을 적극 검토한 적이 있다.

5-2. 메모리 반도체 시장에 치우친 국내 시장

반도체는 2011년부터 한국 최대 수출 품목으로 자리 잡았다. 하지만 통계청 자료에 의하면, 2018년 12월부터 연속 마이너스 수출을 기록하고 있다. 다만 '빅데이터(Big Data)', '인공지능(AI)', 'IoT', '자율주행', '5G 통신 서비스'가 확대되면서, 빅데이터 처리 성능 향상을 위한 서버용 'DRAM', '낸드 플래시 메모리(NAND Flash Memory)' 등의 수요는 지속적으로 발생하고 있음에 따라, 메모리 반도체 시장은 회복될 것으로 전망된다.

또한 기존 자동차와 의료기기 등에 IT 기술이 결합되어 사용자의 편의성과 안정성을 고려한 다양한 '스마트융합제품(인공지능, 로보틱스, 자율주행차, 웨어러블 디바이스 등)'이 출시되어, 연산처리 및 제어용 비메모리 반도체 수요도 증가하고 있다. 2019년 기준 세계 반도체 시장의 70% 이상은 '비메모리 반도체'였다. 국내 반도체 시장이 메모리 반도체로 편중된 점을 개선하기 위해, 정부 차원에서 R&D 지원 및 전문 인력을 유치를 위해 다양한 정책을 마련하고 있다.

중국 기업들이 메모리 반도체 시장에 진입하면서, 메모리 중심의 사업구조를 비메모리 분야로 확대하기 위해, 최근 국내 반도체 업체들은 메모리 반도체 호황에 따른 영업이익을 바탕으로 비메모리 반도체 분야로 사업영역을 확장하고 있다. 2019년에 삼성전자는 '반도체 비전 2030'을 제시하며, 반도체 제조 인프라와 기술력을 공유해서 '팹리스(Fabless)', '디자인하우스(Design House)' 등 국내 중소업체와 협력을 강화하여, 전체 반도체 산업 생태계의 경쟁력을 향상시킬 계획이라고 발표하였다.

6. '반도체 공정' 관련 기업

반도체는 나노미터 크기의 영역에서 회로를 설계한다. 반도체를 구성하는 '트랜지스터(Transistor)', '커패시터(Capacitor)', '회로 배선(Circuit Wiring)' 등의 크기를 소형화시켜 한정된 크기의 실리콘 웨이퍼에 더 많은 칩을 생산하기 위하여 지속적으로 기술이 개발되고 있다. 최근 '파운드리(Foundry)' 업체는 회로 배선 폭을 수 nm로 설계·제작 가능하도록 생산 기술을 개발하여, '팹리스(Fabless)' 업체들에게 제공하고 있다. '모바일 기기', '디지털 가전 기기', '자동차', '첨단의료 기기' 등에서 광범위하게 활용될 수 있도록 다기능을 집적한 '시스템 반도체'를 생산하기 위해 '적층 구조 방식'의 기술도 발전하는 등 '전 공정(Front-End Process)' 단계에서부터 '후 공정(Back-End Process)'까지 전반적으로 기술 개발이 이루어지고 있다.

- '파운드리(Foundry)' 업체: '파운드리' 업체란 반도체 산업에서 외부 업체가 설계한 반도체 제품을 위탁받아 생산·공급하는, 공장을 가진 반도체 위탁 생산 회사이다., 공장을 가진 반도체 위탁 생산 회사를 말한다.

- '팹리스(Fabless) 업체: '팹리스' 업체란 반도체 제조 공정 중 설계와 개발을 전문화한 회사를 말한다.

일반적으로 반도체 제조공정에서는 '고가의 설비', '부대시설', '원료로 사용되는 화학물질의 공급 시스템', '클린룸(Clean Room)' 등의 다수의 장치가 종합적으로 사용되고 있다. '빅데이터(Big Data)' 및 'IoT' 기술이 발전함에 따라, 대용량의 데이터를 처리·저장해야 하는 반도체의 수요가 급증하고 있다. 이에 초저전력 및 소형화 반도체를 제조하기 위해 '회로 패턴 미세화 공정'을 비롯하여, '적층 방식'으로 메모리 반도체를 생산하는데 필요한 장비·기술을 개발하는 유수의 업체들이 존재한다.

6-1. TSMC

- 국적: 대만

- 분야: 파운드리 전문 업체

TSMC는 반도체 위탁 생산 전문 업체로서, 명실공히 세계 1위의 파운드리 기업이다. 글로벌 시장조사 업체 '트렌드포스(TrendForce)' 자료에 따르면, 2022년 1분기 파운드리 점유율은 TSMC가 53.6%로 높은 비중을 차지하고 있다. 2018년 말 '불화 아르고(ArFi)' 노광 방식을 통해 반도체 전자회로의 선폭 크기가 7nm 이하인 기술 개발에 성공하여 '애플(Apple)', '하이실리콘(HiSilicon)', '퀄컴(Qualcomm)' 등의 물량을 수주하면서 해당 시장을 선점했다.

TSMC는 '타이난(Tainan)'의 '사이언스 파크(Science Park)'에 위치한 공장에서 '극자외선(EUV: Extreme Ultra Viloet)' 노광 방식을 통해 5nm 이하인 반도체 제공 공정을 2020년부터 양산에 돌입하였다. 또한 2018년부터 타이난 지역에 건설 중인 3nm 파운드리 공장 설립에도 지속적으로 투자하고 있다. 2022년 하반기부터는 3나노 반도체 양산을 시작했다. 이처럼 TSMC는 나노 반도체 양산 체제를 갖추기 위해 로드맵을 제시하며, 파운드리 업체 분야에서 경쟁사와 격차를 더욱 벌리기 위해 매진하고 있다. 'R&D(Research and Development)' 센터에서는 2nm 공정에 개발에 착수하였다.

6-2. SMIC

- 국적: 중국

- 분야: 파운드리 전문업체

중국의 반도체 파운드리 전문 업체 'SMIC(Semiconductor Manufacturing International Corporation)'는 2019년 하반기부터 14nm 'Fin-FET(Field Effect Transistor)' 공정 양산을 시작하면서, TSMC와의 파운드리 기술 격차를 줄이고 있다. 일반적으로 반도체 전자회로의 선폭 크기 단위인 나노 숫자가 낮아질수록 미세한 회로 공정이 가능하여 반도체를 소형화할 수 있고 전력효율을 높일 수 있지만, 생산단가가 높아진다. 이러한 점을 고려하여 상대적으로 저렴한 14nm 공정을 선호하는 기업들이 있다. SMIC는 이러한 시장을 공략하면서 중국 반도체 자급률을 높이고 있다.

6-3. 마이크론(MICRON)

- 국적: 미국

- 분야: 메모리 반도체

'마이크론(MICRON)'은 '삼성전자', 'SK하이닉스'와 함께 메모리 반도체 'Big3' 구도를 형성하고 있는 기업이다. 2019년에는 8Gb DDR 4 DRAM 보다 전력 소모가 약 40% 적은 3세대 10nm급 16Gb DDR4 DRAM 양산을 시작하였다. 또한 적층 구조인 96단 '3D 낸드 프래시 메모리(NAND Flash Memory)'를 생산하기 위해, 2019년에는 '싱가포르'에 '낸드 플래시 메모리(NAND Flash Memory)' 반도체 공장을 준공하는 등 공격적으로 인프라에 투자하고 있다.

6-4. 삼성전자

- 국적: 한국

- 분야: 메모리 반도체

'삼성전자'는 2023년 기준, 메모리 반도체 분야의 세계 1위 업체로서, 반도체 제조 공정에 대규모로 투자하고 있다. 2018년에 EUV 노광 방식을 통해 7nm 공정 기술을 상용화하였고, 최근에는 5nm 공정 개발에 성공하여 기존 7nm 공정 대비 회로 면적을 25%, 전력효율을 10% 이상 개선하는 등 초미세 공정에 대한 기술경쟁력을 확보하였다. 이러한 기술력을 기반으로 '퀄컴(Qualcomm)' 및 'IBM', 'AMD', '엔비디아(Nvidia)' 등 글로벌 IT기업의 물량을 수주하면서 '파운드리' 시장 점유율을 높이고 있다.

주력 제품인 '메모리 반도체' 제조 기술에도 공격적으로 투자한 결과, 2013년부터 V-NAND 기술의 상용화하여, 적층 구조의 '낸드 플래시 메모리(NAND Flash Memory)' 반도체를 상용화하였다. 또 최근에는 '싱글 스택(Single Stack)' 방식으로 한 웨이퍼 상에 반도체 칩을 100단 이상 적층하는 기술을 개발하여 경쟁사와의 기술 격차를 더욱 벌렸다. 2014년부터는 'TSV(Through Silicon Via)' 기술을 적용하여 적층구조의 DDR4 DRAM을 생산하기 시작했다. 또 2020년에는 'EUV 노광 공정'을 이용해 반도체 크기 및 전력효율 등을 개선한 DRAM을 세계 최초로 출시하였다. 또 2019년에는 '울산과학기술원(UNIST: Ulsan National Institute of Science and Technology)'과 협업하여 기존 반도체 성능을 향상시킨 '3진법 금속-산화막 반도체(Ternary Metal-Oxide-Semiconductor)' 제조 기술을 개발하는데 성공했다.

6-5. SK하이닉스(SK hynix)

- 국적: 한국

- 분야: 메모리 반도체

'SK하이닉스(SK hynix)'는 '메모리 반도체' 선도 기업으로 '낸드 플래시 메모리(NAND Flash Memory)'와 'DRAM' 제조 공정 기술을 지속적으로 개발하고 있다. 일반적으로 NAND 플래시 메모리는 데이터가 저장되는 메인부인 'Cell'과 Cell의 동작을 제어하는 주변부 회로 'Peri'로 구성되어 있다. Peri를 Cell 아래에 배치해서 반도체의 크기 및 전력 효율 등을 개선시키는 'PUC(Peri Under Cell)' 기술을 자체 개발하였다. 2019년에는 'PUC(Peri Under Cell)' 기술을 기반으로, 96단 512Gb급 'TLC(Triple Level Cell)' 4D NAND 플래시 메모리를 세계 최초로 개발하는 데 성공하였다.

6-6. 에이티세미콘(ATsemicon)

- 국적: 한국

'에이티세미콘(ATsemicon)'은 '반도체 테스트'와 '패키징 서비스(Package Service)'를 제공하는 전문 기업이다. '웨이퍼 프로브 테스트(Wafer Probe Test)', '패키징 공정(Packaging Process)', '최종 검사'까지 제공하는 Turn-key 솔루션을 보유하고 있다. '메모리 반도체(Memory Semiconductor)'와 '시스템 반도체(System Semiconductor)'를 모두 테스트 및 패키징 할 수 있는 기술력을 보유하고 있다. 지속적인 인프라 투자로 회사의 경쟁력을 강화하고 있다. 또한 자체적으로 품질관리 프로그램을 개발해서 불량률을 최소화하여 고객 만족도 향상을 위해 매진하고 있다.