'수확 가속의 법칙(Law of Accelarating Returns)'의 지배를 받는 기술의 범위 중에 가장 널리 알려진 기하급수적 추세의 사례는 이른바 '무어의 법칙(Moore's Law)'이라는 것이다. 1970년대 중반에 집적회로 발명의 선구자이자 향후 '인텔(Intel)'사의 회장이 된 '고든 무어(Gordon Moore, 1923~)'는 집적회로에 집어넣을 수 있는 트랜지스터의 수가 24개월마다 두 배로 늘어난다는 것을 발견했다. (1960년대 중반에는 12개월로 추산했다가 나중에 수정함) 전자들이 이동하는 거리가 짧아지는 것이니, 회로의 동작 속도가 빨라지고, 전체 계산력도 늘어난다. 그 결과 연산의 '가성비(가격 대 성능비)'가 기하급수적으로 증가한다. 정보기술의 역량을 측정하는 여타 잣대들, 가령 가성비, 대역폭, 용량 등의 '배가 속도(2배가 되는 속도)'는 대체로 1~2년 정도다.

0. 목차

- 무어의 법칙

- '무어의 법칙' 추세 확인하기

- '무어의 법칙'은 지속 가능한가?

1. 무어의 법칙

'고든 무어(Goldon Moore)'는 1965년 4월 19일자 '일렉트로닉스'에 다음과 같은 글을 썼다. "집적 전자공학의 미래가 곧 전자공학의 미래다." 집적 기술은 전자공학의 융성을 가져올 것이고, 이 과학이 수많은 새로운 영역으로 번지게 할 것이다. 아울러 새로운 과학이 얼마나 대단한지 독자들에게 절절히 알려주기 위해, '골든 무어'는 이렇게 덧붙였다. "경제의 추진력은 실로 대단하므로, 1975년이면 하나의 실리콘칩에 65000개의 소자가 밀어넣어지게 될지도 모른다."

'골든 무어'는 하나의 '집적회로에 들어가는 트랜지스터의 수가 매년 두 배씩 늘었다'고 지적했다. 소위 '무어의 법칙(Moore's Law)'이라고 불리게 된 1965년의 예측은 당시 비판을 많이 받았다. 칩당 트랜지스터 수를 표기한 로그 함수 도표에 데이터가 5개밖에 없었기 때문이다. (1959년에서 1965년까지였다.) 막 정체를 드러낸 이 추세를 1975년까지 연장하는 것은 무모해 보였다. 실제 '골든 무어'의 초기 예측은 들어맞지 않았고, 10년 뒤에 그는 예측치를 다소 하향 조정하여 발표했다. 하지만 기본적인 발상, 집적회로에 들어가는 트랜지스터의 크기가 줄어듦에 따라 전자기기의 '가성비(가격 대 성능비)'가 기하급수적으로 증가하리라는 생각은 유효한 선견지명이었다. 무어의 법칙이 종말을 맞이할 거라는 예측은 끊이지 않았다. 하지만 이 놀랍게도 무어의 법칙의 종말은 계속 뒤로 미뤄지고 있다.

2. '무어의 법칙' 추세 확인하기

좁게 해석한 무어의 법칙은 고정된 크기의 집적회로에 들어가는 트랜지스터의 개수를 다루는 것이다. 그보다 더 좁게는 트랜지스터의 회로 선폭을 나타내기도 한다. 하지만 '가성비(가격 대 성능비)'를 가장 적절하게 반영하는 척도는 다양한 층위의 '영리함'을 고려하고 있는 단위 비용당 연산 속도일 것이다.

2-1. DRAM '하프 피치(회로 선폭)'

'무어의 법칙'의 주요 원동력은 반도체의 '회로 선폭'이 줄어드는 것이다. '회로 선폭(feature size)'는 반도체 칩에서 적용되는 회로들 사이의 배선폭 혹은 게이트의 크기를 말하는 것으로 '하프 피치(Half Pitch)'라고도 한다. 이것을 줄일수록 집적도와 속도가 높아지고 소비 전력도 줄어든다. 선폭은 각 차원별로 5.4년마다 반으로 줄어든다. 칩은 기능적으로 2차원이므로 2제곱밀리미터당 구성 요소의 개수가 2.7년마다 두배씩 증가한다는 계산이 나온다.

| 년도(Year) | DRAM Half Pitch (nm) |

| 1967 | 13000 |

| 1969 | 1000 |

| 1981 | 2000 |

| 1983 | 1600 |

| 1987 | 1000 |

| 1990 | 900 |

| 1993 | 800 |

| 1995 | 400 |

| 1997 | 250 |

| 1999 | 200 |

| 2001 | 130 |

| 2002 | 115 |

| 2003 | 100 |

| 2004 | 90 |

| 2005 | 80 |

| 2006 | 70 |

| 2007 | 65 |

| 2010 | 45 |

| 2013 | 32 |

| 2016 | 22 |

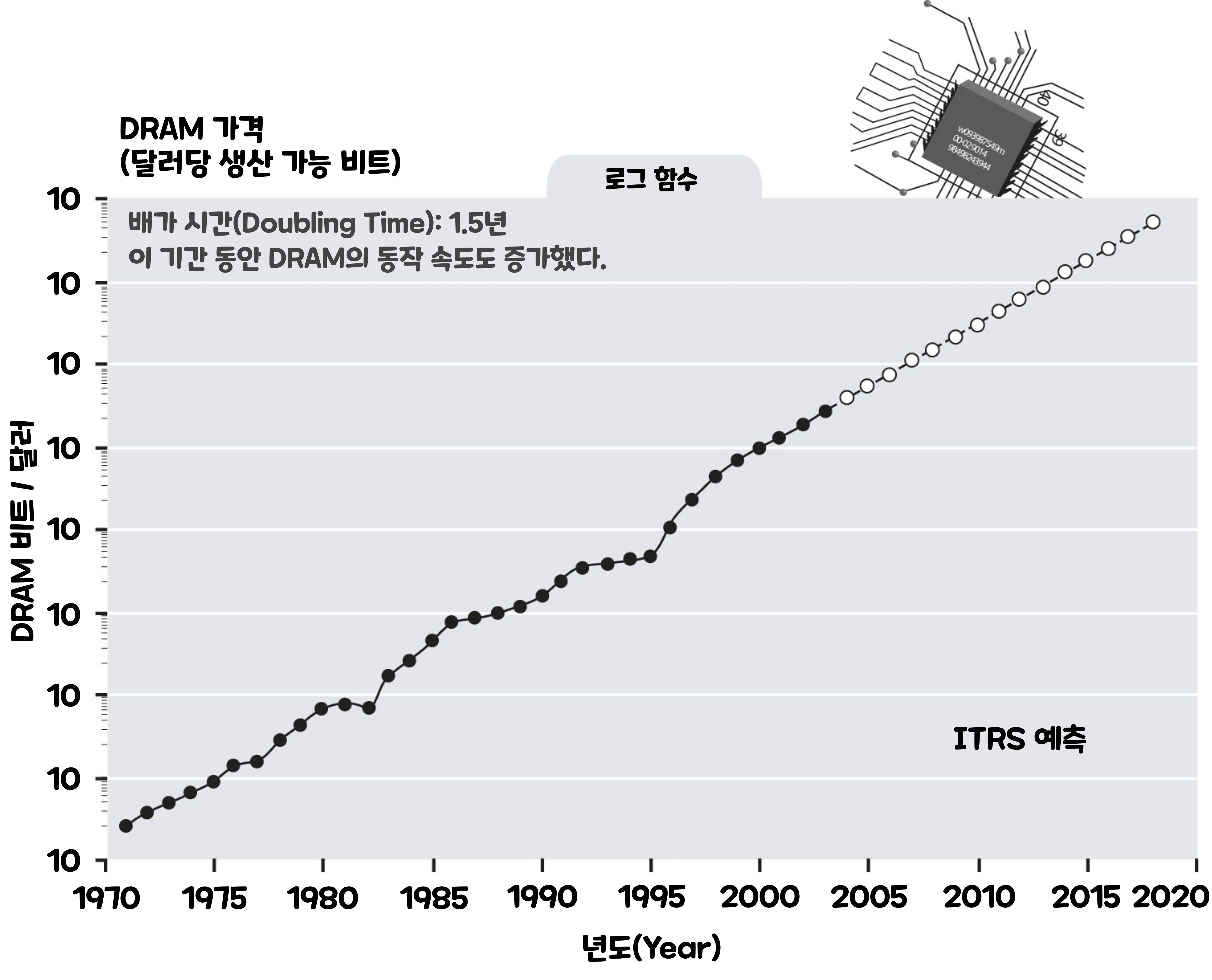

2-2. DRAM 가격 (달러당 생산 가능 비트)

'동적 임의 접속 기억 장치(DRAM: Dynamic Random Access Memory)'란 컴퓨터의 주 기억 장치인 RAM의 일종으로 '정적 기억 장치(SRAM)'에 비해 가격이 낮고 집적도가 매우 높아 대용량 기억 장치로 널리 사용된다. 'DRAM'의 제곱 밀리 미터당 제작 비용도 하락하고 있다. 달러당 DRAM의 배가 시간은 1.5년밖에 되지 않는다.

'트랜지스터(Transistor)'도 비슷한 추세를 따랐다. 1968년에는 1달러로 트랜지스터를 하나 살 수 있었다. 하지만 2002년에는 1달러로 약 1000만 개 정도를 살 수 있다. DRAM은 기술 혁신을 주도하는 특수한 분야이기 때문에, 평균적인 트랜지스터 가격의 반감기는 DRAM보다 약간 느린 1.6년이다.

| 년도(Year) | DRAM 비트 / 달러 (DRAM Bit / Dollar) |

| 1971 | 252 |

| 1972 | 378 |

| 1973 | 490 |

| 1974 | 667 |

| 1975 | 861 |

| 1976 | 1460 |

| 1977 | 1430 |

| 1978 | 2780 |

| 1979 | 4380 |

| 1980 | 6900 |

| 1981 | 6880 |

| 1982 | 6680 |

| 1983 | 16400 |

| 1984 | 25600 |

| 1985 | 45800 |

| 1986 | 70200 |

| 1987 | 80900 |

| 1988 | 91800 |

| 1989 | 1080000 |

| 1990 | 145000 |

| 1991 | 229000 |

| 1992 | 330000 |

| 1993 | 368000 |

| 1994 | 418000 |

| 1995 | 444000 |

| 1996 | 1060000 |

| 1997 | 2310000 |

| 1998 | 4900000 |

| 1999 | 6930000 |

| 2000 | 9820000 |

| 2001 | 13000000 |

| 2002 | 18500000 |

| 2003 | 26300000 |

| 2004 | 37000000 |

| 2005 | 52600000 |

| 2006 | 71400000 |

| 2007 | 104000000 |

| 2008 | 143000000 |

| 2009 | 200000000 |

| 2010 | 294000000 |

| 2011 | 417000000 |

| 2012 | 588000000 |

| 2013 | 833000000 |

| 2014 | 1250000000 |

| 2015 | 1670000000 |

| 2016 | 2500000000 |

| 2017 | 3330000000 |

| 2018 | 5000000000 |

2-3. 평균 트랜지스터 가격

반도체의 가격 대 성능비가 부드럽게 가속한 것은 점점 더 작은 규모로 나아가며 발전한 일련의 기술 덕택이다. 최신의 회로 제조 공정은 '나노기술' 수준으로 이미 '10나노미터(10nm)' 아래로 내려갔다. 트랜지스터는 더 작아지고 저렴해지면서, 그에 따라 전자의 이동 거리가 짧아지면서 지난 30년간 속도가 약 1000배 빨라졌다.

| 년도(year) | 평균 트랜지스터 가격 |

| 1968 | 1 |

| 1969 | 0.85 |

| 1970 | 0.6 |

| 1971 | 0.3 |

| 1972 | 0.15 |

| 1973 | 0.1 |

| 1974 | 0.07 |

| 1975 | 0.028 |

| 1976 | 0.015 |

| 1977 | 0.008 |

| 1978 | 0.005 |

| 1979 | 0.002 |

| 1980 | 0.0013 |

| 1981 | 0.00082 |

| 1982 | 0.0004 |

| 1983 | 0.00032 |

| 1984 | 0.00032 |

| 1985 | 0.00015 |

| 1986 | 0.00009 |

| 1987 | 0.000081 |

| 1988 | 0.00006 |

| 1989 | 0.000035 |

| 1990 | 0.00002 |

| 1991 | 0.000017 |

| 1992 | 0.00001 |

| 1993 | 0.000009 |

| 1994 | 0.000008 |

| 1995 | 0.000007 |

| 1996 | 0.000005 |

| 1997 | 0.000003 |

| 1998 | 0.0000014 |

| 1999 | 0.00000095 |

| 2000 | 0.0000008 |

| 2001 | 0.00000035 |

| 2002 | 0.00000026 |

2-4. 트랜지스터 제조 비용

'트랜지스터 제조 비용(Transistor Manufacturing Cost)'도 지속적으로 감소해왔다.

| 년도(Year) | 1 | 0.7 | 0.5 | 0.35 | 0.25 | 0.18 | 0.13 | 0.09 | 0.065 |

| 1990 | 22.5 | 11.2 | 8.8 | ||||||

| 1991 | 21.9 | 10.3 | 7.3 | ||||||

| 1992 | 21.4 | 9.9 | 5.9 | ||||||

| 1993 | 20.8 | 9.7 | 4.7 | 4 | |||||

| 1994 | 9.4 | 4.3 | 3 | ||||||

| 1995 | 8.9 | 3.9 | 2.3 | ||||||

| 1996 | 8.5 | 3.6 | 1.8 | 1.5 | |||||

| 1997 | 3.2 | 1.6 | 1.2 | ||||||

| 1998 | 3.3 | 1.4 | 0.8 | 0.7 | |||||

| 1999 | 2.8 | 1.4 | 0.8 | 0.5 | |||||

| 2000 | 1.3 | 0.7 | 0.4 | 0.3 | |||||

| 2001 | 1 | 0.7 | 0.3 | 0.2 | |||||

| 2002 | 0.8 | 0.6 | 0.3 | 0.2 | |||||

| 2003 | 0.6 | 0.3 | 0.2 | 0.1 | |||||

| 2004 | 0.4 | 0.3 | 0.1 | 0.1 | |||||

| 2005 | 0.4 | 0.3 | 0.1 | 8.5 | |||||

| 2006 | 0.3 | 0.1 | 6.8 | 0.05 | |||||

| 2007 | 0.25 | 0.1 | 6.1 | 4.2 | |||||

| 2008 | 9.9 | 5.6 | 3.3 | ||||||

| 2009 | 0.1 | 5 | 2.7 | ||||||

| 2010 | 4.7 | 2.5 |

2-5. 마이크로프로세서 클럭 속도

'마이크로프로세서 클럭 속도(Microprocessor Clock Speed)'의 발전도 가격대 성능비를 끌어올려왔다.

| 년도(Year) | Microprocessor Clock Speed (Hz) |

| 1976 | 1350000 |

| 1977 | 2060000 |

| 1978 | 2140000 |

| 1979 | 2290000 |

| 1980 | 1940000 |

| 1981 | 2410000 |

| 1982 | 2630000 |

| 1983 | 4070000 |

| 1984 | 5190000 |

| 1985 | 5890000 |

| 1986 | 7210000 |

| 1987 | 9430000 |

| 1988 | 12660000 |

| 1989 | 15630000 |

| 1990 | 19440000 |

| 1991 | 21180000 |

| 1992 | 29030000 |

| 1993 | 34150000 |

| 1994 | 53380000 |

| 1995 | 78040000 |

| 1996 | 140500000 |

| 1997 | 184280000 |

| 1998 | 337000000 |

| 1999 | 413680000 |

| 2001 | 1684000000 |

| 2002 | 2317000000 |

| 2003 | 3088000000 |

| 2004 | 3990000000 |

| 2005 | 5173000000 |

| 2006 | 5631000000 |

| 2007 | 6739000000 |

| 2010 | 11511000000 |

| 2013 | 19348000000 |

| 2016 | 28751000000 |

2-6. 트랜지스터의 처리 주기당 마이크로프로세서 비용

가격은 기하급수적으로 낮아지면서 처리 속도는 기하급수적으로 빨라지니, 트랜지스터의 처리 주기당 비용의 반감기는 1.1년에 불과하다. 트랜지스터의 처리 주기당 비용은 속도와 용량을 모두 고려한 것이므로 가격 대 성능비를 더 정확히, 종합적으로 측정한 것이다. 이 트랜지스터 처리 주기당 비용은 더 높은 설계 차원에서의 연산 효율' 개선은 고려하지도 않은 것이다. 여기서 '더 높은 설계 차원에서의 연산 효율'이란 예컨대 '마이크로프로세서 설계 혁신' 등을 말하는 것이다.

| 년도(Year) | $ / Transistor / Hz |

| 1976 | 0.00000001111 |

| 1977 | 0.000000003883 |

| 1978 | 0.000000002336 |

| 1979 | 0.0000000008734 |

| 1980 | 0.0000000006701 |

| 1981 | 0.0000000003402 |

| 1982 | 0.0000000001521 |

| 1983 | 0.00000000007862 |

| 1984 | 0.00000000006166 |

| 1985 | 0.00000000002547 |

| 1986 | 0.000000000001238 |

| 1987 | 0.000000000000859 |

| 1988 | 0.0000000000004739 |

| 1989 | 0.0000000000002239 |

| 1990 | 0.0000000000001029 |

| 1991 | 8.026E-13 |

| 1992 | 3.445E-13 |

| 1993 | 2.635E-13 |

| 1994 | 1.499E-13 |

| 1995 | 8.97E-14 |

| 1996 | 3.559E-14 |

| 1997 | 1628E-14 |

| 1998 | 4.154E-15 |

| 1999 | 2.296E-15 |

| 2001 | 2.078E-16 |

| 2002 | 1.122E-16 |

| 2003 | 1.716E-17 |

| 2004 | 9.524E-17 |

| 2005 | 5.219E-17 |

| 2006 | 3.374E-17 |

| 2007 | 1.974E-17 |

| 2010 | 4.092E-18 |

| 2013 | 8.58E-10 |

| 2016 | 2.052E-19 |

2-7. 마이크로프로세서 당 트랜지스터 개수

'인텔 프로세서(Intel Processor)'의 트랜지스터 개수는 2년마다 배가 되어왔다.

| 도입 연도(Year of Introduction) | 트랜지스터(Transistor) | 프로세서(Processor) |

| 1971 | 2250 | 4004 |

| 1972 | 2500 | 8008 |

| 1974 | 5000 | 8080 |

| 1978 | 29000 | 8086 |

| 1982 | 120000 | 286 |

| 1985 | 275000 | 386TM processor |

| 1989 | 1600000 | 486TM DX processor |

| 1993 | 3100000 | Pentium processor |

| 1997 | 7500000 | Pentium 2 processor |

| 1999 | 24000000 | Pentium 3 processor |

| 2000 | 42000000 | Pentium 4 processor |

| 2002 | 169000000 | Xeon |

| 2003 | 410000000 | Itanium |

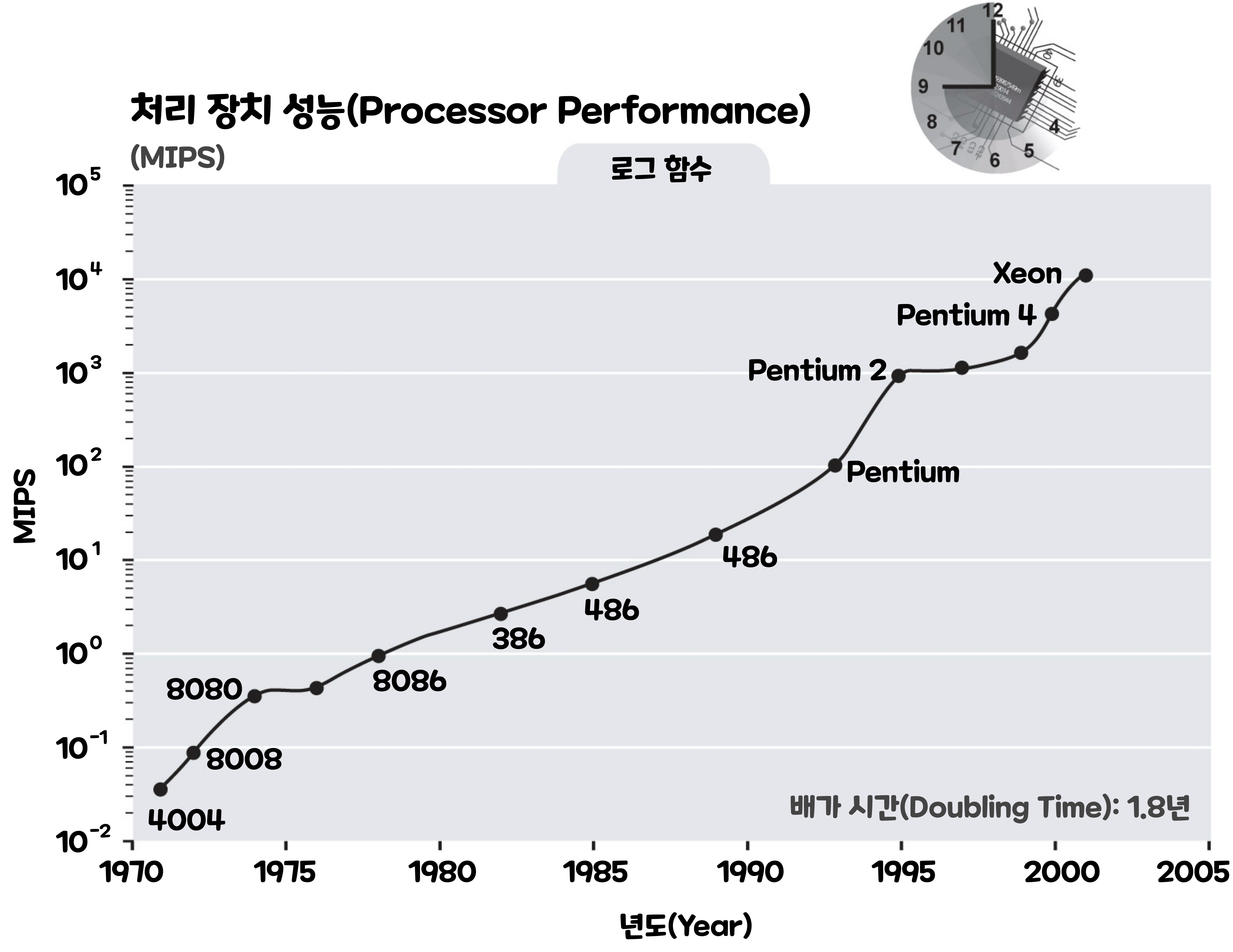

2-8. 처리 장치 성능(MIPS)

MIPS 단위로 측정한 처리 장치 성능은 처리 장치당 1.8년마다 배가되어왔다.

| 년도(Year) | MIPS |

| 1971 | 0.035 |

| 1972 | 0.08 |

| 1974 | 0.33 |

| 1976 | 0.4 |

| 1978 | 0.9 |

| 1982 | 2.5 |

| 1985 | 5 |

| 1989 | 17 |

| 1993 | 100 |

| 1995 | 800 |

| 1997 | 1005 |

| 1999 | 1500 |

| 2000 | 4000 |

| 2001 | 10000 |

| 2002 | 12000 |

2-9. 판매된 총 비트

정보기술의 비용은 크게 하락했지만, 한편으로 수요는 그보다 더 빠르게 증가했다. 판매된 '비트(bit)' 수는 1.1년마다 두 배로 늘어 비트당 비용의 반감기인 1.5년보다 빠른 속도로 보여줬다.

결과적으로 반도체 산업은 1958년부터 2002년까지 매년 총 수입 면에서 18%의 성장을 누려왔다. 전체 정보기술 산업은 1977년 국내 총생산의 4.2%를 차지했으나, 1998년에는 8.2%로 성장했다. 정보기술의 영향력은 모든 경제 분야에서 점점 커지고 있다. 대부분의 제품과 서비스의 가치 중 정보기술이 기여하는 바가 빠르게 증가하고 있다. 탁자나 의자 같은 일반적인 제품 조차도 정보 내용을 가지고 있다.

| 년도(Year) | 판매된 총 비트(Total Bits Shipped) |

| 1971 | 921600000 |

| 1972 | 3788800000 |

| 1973 | 8294400000 |

| 1974 | 19865600000 |

| 1975 | 42700800000 |

| 1976 | 130662400000 |

| 1977 | 276070400000 |

| 1978 | 663859200000 |

| 1979 | 1438720000000 |

| 1980 | 3172761600000 |

| 1981 | 4512665600000 |

| 1982 | 11520409600000 |

| 1983 | 29648486400000 |

| 1984 | 68418764800000 |

| 1985 | 87518412800000 |

| 1986 | 192407142400000 |

| 1987 | 255608422400000 |

| 1988 | 429404979200000 |

| 1989 | 631957094400000 |

| 1990 | 950593126400000 |

| 1991 | 1.5465906176E+15 |

| 1992 | 2.845638656E+15 |

| 1993 | 4.1779593216E+15 |

| 1994 | 7.5108057088E+15 |

| 1995 | 1.3010599936E+16 |

| 1996 | 2.3359078006784E+16 |

| 1997 | 4.5653879160832E+16 |

| 1998 | 8.5176878104576E+16 |

| 1999 | 1.47327404736512E+17 |

| 2000 | 2.63635863601152E+17 |

| 2001 | 4.19671970100019E+17 |

| 2002 | 5.9000909463552E+17 |

3. '무어의 법칙'은 지속 가능한가?

3-1. '무어의 법칙'은 자기 성취적 예언에 불과한가?

'무어의 법칙'은 자기 성취적 예언에 불과하다고 주장하는 사람들도 있다. 실제로 산업 관계자들은 미래 어느 특정 시기에 어느 만큼의 성과를 달성하고 싶은지 미리 정해두고, 그에 맞는 연구 개발을 준비한다. 해당 산업의 '로드맵(Road Map)'이란 것이 그런 준비다.

하지만 정보기술의 기하급수적 추세는 무어의 법칙이 다루는 영역보다 더 광범위하다. 본질적으로 정보를 다루는 모든 기술에서, 모든 측정의 측면에서 이와 동일한 추세가 나타난다. '가성비(가격 대 성능비)'가 가속된다는 것을 전혀 인식할 수 없었던 분야, 혹은 명확히 표현되지 않았던 분야의 기술도 포함된다. 연산 자체만 보더라도 단위 비용당 성능 성장은 '무어의 법칙'이 예측하는 것보다 훨씬 광범위한 활동들을 통해 일어나고 있다.

3-2. '무어의 법칙'은 하나의 패러다임에 불과한가?

그러면 '무어의 법칙'은 하나의 패러다임에 불과할까? 다시 말해 현재 '집적회로(Intergrated Circuit)'라는 패러다임이 한계에 부딪히면, 무어의 법칙은 종말을 고하지 않을까? 이에 대한 답부터 말하자면, 집적회로라는 패러다임에서 무어의 법칙이 끝날 일은 없다.

'수확 가속의 법칙(Law of Accelarating Returns)'에 따라 '패러다임의 전환(혁신)'은 개별 패러다임의 S자 곡선을 연속적인 기하급수적 증가로 바꿔준다. 20세기의 유명한 49개 연산 시스템 및 컴퓨터 들의 '가성비(가격 대 성능비)'를 100고정 달러당 초당 명령을 기준으로 측정한 뒤 그래프로 나타내보면 이러한 패턴을 명확히 알 수 있다. 낡은 패러다임이 내재적 한계에 이르면, 새로운 패러다임이 이어진다. '무어의 법칙'은 연산 시스템의 하나의 패러다임이 아니다. 그림에서도 알 수 있듯이 '집적회로'가 발명되기 훨씬 전부터 연산의 가격 대 성능비를 기하급수적으로 증가시켜준 4개의 다른 패러다임들이 있었다. 그것은 바로 순서대로 '전기기계식 컴퓨터(Electromechanical Computer)', '계전기식 컴퓨터(Relay System Computer)', '진공관(Vacuum Tube)', '트랜지스터(Transistor)'였다. 이번 패러다임도 마지막이 아니다. '집적회로' 패러다임의 S자 곡선의 끝에 다다르면, 기하급수적 성장은 6번째 패러다임인 '삼차원 분자 연산(3D Molecular Calculation)'으로 이어질 것이다.

'3차원 연산 시스템'은 선택의 문제가 아니라 2차원에서 연속적으로 이어질 자연스러운 발전이다. 생물학적 지능의 경우, 인간의 피질은 사실상 평면이나 마찬가지다. 여섯 개의 얇은 층이 정교하게 접혀서 표면적을 극대화하는 구조로 되어 있다. 접힌 구조 또한 3차원을 이용하는 방법이다. '프랙탈 시스템'에서 정교하게 접힌 구조는 중간적 차원값을 갖는 것으로 여겨진다. 그런 시각에서 보면, 복잡한 평면이라 할 수 있는 인간의 피질은 2차원과 3차원 사이의 다양한 차원값을 갖는다고 말할 수 있다. 다른 뇌 구조들, 가령 소뇌는 3차원 구조이지만 2차원 구조가 반복적으로 쌓인 형태다. 미래의 연산 시스템은 고도로 접힌 2차원과 완벽한 3차원을 결합한 것이 될 가능성이 높다.

| 년도(Year) | CPS / $1000 | Device |

| 1900 | 0.000005821 | Analytical Engine |

| 1908 | 0.0001299 | Hollerith Tabulator |

| 1911 | 0.00005787 | Monroe Calculator |

| 1919 | 0.001064 | IBM Tabulator |

| 1928 | 0.0006993 | National Ellis 3000 |

| 1939 | 0.008547 | Zuse 2 |

| 1940 | 0.1431 | Bell Calculator Model 1 |

| 1941 | 0.0463 | Zuse 3 |

| 1943 | 5.308 | Colossus |

| 1946 | 0.7981 | ENIAC |

| 1948 | 0.3698 | IBM SSEC |

| 1949 | 1.837 | BINAC |

| 1949 | 1.044 | EDSAC |

| 1951 | 1.43 | Univac 1 |

| 1953 | 6.104 | Univac 1103 |

| 1954 | 0.3669 | EDVAC |

| 1955 | 16.45 | Whirlwind |

| 1955 | 3.438 | IBM 704 |

| 1958 | 0.3257 | Datamatic 1000 |

| 1958 | 0.9144 | Univac 2 |

| 1960 | 1.514 | IBM 1620 |

| 1960 | 151.5 | DEC PDP-1 |

| 1961 | 282.5 | DEC PDP-4 |

| 1962 | 29.43 | Univac 3 |

| 1964 | 158.6 | CDC 6600 |

| 1965 | 482.6 | IBM 1130 |

| 1965 | 1792 | DEC PDP-8 |

| 1966 | 49.72 | IBM 360 Model 75 |

| 1968 | 213.6 | DEC PDP-10 |

| 1973 | 728.6 | Intellec-8 |

| 1973 | 3401 | Data General Nova |

| 1975 | 10580 | Altair 8800 |

| 1976 | 777 | DEC PDP-11 Model 70 |

| 1977 | 3720 | Cray 1 |

| 1977 | 26870 | Apple 2 |

| 1979 | 1114 | DEC VAX 11 Model 780 |

| 1980 | 5621 | Sun-1 |

| 1982 | 126600 | IBM PC |

| 1982 | 126600 | Compaq Portable |

| 1983 | 86280 | IBM AT-80286 |

| 1984 | 85030 | Apple Macintosh |

| 1986 | 538200 | Compaq Deskpro 386 |

| 1987 | 232600 | Apple Mac 21993 |

| 1993 | 3549000 | Pentium PC |

| 1996 | 48080000 | Pentium PC |

| 1998 | 133300000 | Pentium 2 PC |

3-3. 물리적으로 연산의 한계에 다다르지는 않을까?

그러면 물리적으로 연산의 한계에 다다르지는 않을까? 즉, 연산을 뒷받침하는 물질과 에너지의 역량에는 내재적 제약이 있어 '무어의 법칙'이 깨질 가능성은 없을까? 이에 대한 답은 '적어도 이번 세기말까지는 그 한계에 다다를 일은 없을 것이다'라는 것이다. 연산의 성장은 그 하위 패러다임을 뛰어넘는 것이며, 현재로서는 계속 기하급수적일 것이라고 보아도 무리가 없다.